Подписка нановости

Новости получают: 231 человек(а)Ежедневная подписка на новости

Предлашаем Вам подписаться на ежедневную рассылку нашего портала. Вы сможете ежедневного получать самые свежие новости мира спутникового и эфирного телевидения, обновления на спутниках и профессиональные обзоры техники».

Правила пользователя

На сайте строго запрещено:

1.1 - сообщения, не относящиеся к содержанию статьи или к контексту обсуждения

1.1.1 - постить сообщения не содержащие смысла (lol , :-) и т.д.)

1.2 - оскорбление и угрозы в адрес посетителей сайта

1.3 - в комментариях, личных сообщениях и постах форума - запрещаются выражения, содержащие ненормативную лексику, унижающие человеческое достоинство, разжигающие межнациональную рознь. Запрещены любые упоминания о политике, фотографии, карикатуры, анекдоты и прочее.

1.4 - СПАМ, а также реклама любых товаров и услуг, иных ресурсов, СМИ или

событий, не относящихся к контексту обсуждения статьи

1.5 - запрещено публиковать ссылки на любые ресурсы сети во всех постах и

комментариях ,за исключением отведенных тем! Если существует необходимость

опубликовать ссылку по теме, обязательное размещение ссылки под тег HIDE

1.6 - запрещено заливать файлы больше чем 512 кб в промежуточные(не

первые) посты темы

1.7 - запрещено писать в темах без обсуждения (разрешено только постить по теме)

, обсуждение в других темах

1.8 - запрещено дублировать посты и темы

1.9 - запрещены сообщения в личку или в icq , за исключением вопросов по

работе форума и сайта

1.10 - красный цвет может использовать только

администрация форума, исключением является выделение очень важных

моментов, которые обязательно выполнить, например при прошивке ресивера.

1.11 - На форуме и сайте разрешено использование изображений только загруженных

непосредственно на форум , другие изображения будут удаляться

1.11.1 На форуме запрещено загружать изображения которые не относятся к

спутниковой тематике, разрешено вставлять изображения из других источников,

возможно размещение только под HIDE

По настоятельной рекомендации с насущными вопросами заходить сразу в раздел Вопросы

новичков о Сат ТВ

RISC

Наборы инструкций в более ранних архитектурах, для облегчения ручного написания программ на языках ассемблеров или прямо в машинных кодах, а также для упрощения реализации компиляторов, выполняли как можно больше работы. Нередко в наборы включались инструкции для прямой поддержки конструкций языков высокого уровня. Другая особенность этих наборов — большинство инструкций, как правило, допускали все возможные методы адресации (т. н. «ортогональность системы команд (англ.)») — к примеру, и операнды, и результат в арифметических операциях доступны не только в регистрах, но и через непосредственную адресацию, и прямо в памяти. Позднее такие архитектуры были названы CISC (англ. Complex instruction set computer).

Однако многие компиляторы не задействовали все возможности таких наборов инструкций, а на сложные методы адресации уходит много времени из-за дополнительных обращений к медленной памяти. Было показано, что такие функции лучше исполнять последовательностью более простых инструкций, если при этом процессор упрощается и в нём остаётся место для большего числа регистров, за счёт которых можно сократить количество обращений к памяти. В первых архитектурах, причисляемых к RISC, большинство инструкций для упрощения декодирования имеют одинаковую длину и похожую структуру, арифметические операции работают только с регистрами, а работа с памятью идёт через отдельные инструкции загрузки (load) и сохранения (store). Эти свойства и позволили лучше сбалансировать этапы конвейеризации, сделав конвейеры в RISC значительно более эффективными и позволив поднять тактовую частоту.

В середине 1970-х разные исследователи (в частности, из IBM) показали, что большинство комбинаций инструкций и ортогональных методов адресации не использовались в большинстве программ, порождаемых компиляторами того времени. Также было обнаружено, что в некоторых архитектурах с микрокодной реализацией сложные операции зачастую были медленнее последовательности более простых операций, выполняющих те же действия. Это было вызвано, в частности, тем, что многие архитектуры разрабатывались в спешке и хорошо оптимизировался микрокод только тех инструкций, которые использовались чаще.

Поскольку многие реальные программы тратят большинство своего времени на выполнение простых операций, многие исследователи решили сфокусироваться на том, чтобы сделать эти операции максимально быстрыми. Тактовая частота процессора ограничена временем, которое процессор тратит на выполнение наиболее медленных шагов в процессе обработки любой инструкции; уменьшение длительности таких шагов даёт общее повышение частоты, а также зачастую ускоряет выполнение и других инструкций за счёт более эффективной конвейеризации. Фокусирование на простых инструкциях и ведёт к архитектуре RISC, цель которой — сделать инструкции настолько простыми, чтобы они легко конвейеризировались и тратили не более одного такта на каждом шаге конвейера на высоких частотах.

Позднее было отмечено, что наиболее значимая характеристика RISC в разделении инструкций для обработки данных и обращения к памяти — обращение к памяти идёт только через инструкции load и store, а все прочие инструкции ограничены внутренними регистрами. Это упростило архитектуру процессоров: позволило инструкциям иметь фиксированную длину, упростило конвейеры и изолировало логику, имеющую дело с задержками при доступе к памяти, только в двух инструкциях. В результате RISC-архитектуры стали называть также архитектурами load/store.

Количество инструкций

Нередко слова «сокращённый набор команд» понимаются как минимизация количества инструкций в системе команд. В действительности, инструкций у многих RISC-процессоров больше, чем у CISC-процессоров. Некоторые RISC-процессоры вроде транспьютеров фирмы INMOS (англ.) имеют наборы команд не меньше, чем, например, у CISC-процессоров IBM System/370; и наоборот — CISC-процессор DEC PDP-8 имеет только 8 основных и несколько расширенных инструкций.

На самом деле, термин «сокращённый» в названии описывает тот факт, что сокращён объём (и время) работы, выполняемый каждой отдельной инструкцией — как максимум один цикл доступа к памяти, — тогда как сложные инструкции CISC-процессоров могут требовать сотен циклов доступа к памяти для своего выполнения.

Некоторые архитектуры, специально разработанные для минимизации количества инструкций, сильно отличаются от классических RISC-архитектур и получили другие названия: Minimal instruction set computer (MISC), Zero instruction set computer (ZISC), Ultimate RISC (также называемый OISC), Transport triggered architecture (TTA) и т. п.

Характерные особенности RISC-процессоров

Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды.

Специализированные команды для операций с памятью — чтения или записи. Операции вида «прочитать-изменить-записать» отсутствуют. Любые операции «изменить» выполняются только над содержимым регистров (т. н. архитектура load-and-store).

Большое количество регистров общего назначения (32 и более).

Отсутствие поддержки операций вида «изменить» над укороченными типами данных — байт, 16-битное слово. Так, например, система команд DEC Alpha содержала только операции над 64-битными словами, и требовала разработки и последующего вызова процедур для выполнения операций над байтами, 16- и 32-битными словами.

Отсутствие микропрограмм внутри самого процессора. То, что в CISC-процессоре исполняется микропрограммами, в RISC-процессоре исполняется как обыкновенный (хотя и помещённый в специальное хранилище) машинный код, не отличающийся принципиально от кода ядра ОС и приложений. Так, например, обработка отказов страниц в DEC Alpha и интерпретация таблиц страниц содержалась в так называемом PALcode (Privileged Architecture Library), помещённом в ПЗУ. Заменой PALCode можно было превратить процессор Alpha из 64-битного в 32-битный, а также изменить порядок байтов в слове и формат входов таблиц страниц виртуальной памяти.

Другие архитектуры

За годы после появления архитектуры RISC были реализованы и другие альтернативы — например, VLIW, MISC, OISC, массово-параллельная обработка, систолическая матрица (англ. Systolic array), переконфигурируемые вычисления (англ. Reconfigurable computing), потоковая архитектура (англ. Dataflow architecture).

Суперскалярные архитектуры (первоначально — большие ЭВМ конца 1960-х годов, в микропроцессорах — Sun SPARC, начиная с Pentium использованы в семействе x86). Распараллеливание исполнения команд между несколькими устройствами исполнения, причём решение о параллельном исполнении двух или более команд принимается аппаратурой процессора на этапе исполнения. Эффективное использование такой архитектуры требует специальной оптимизации машинного кода в компиляторе для генерации пар независимых команд (когда результат одной команды не является аргументом другой).

Архитектуры VLIW (very long instruction word — очень длинное слово команды). Отличаются от суперскалярной архитектуры тем, что решение о распараллеливании принимается не аппаратурой на этапе исполнения, а компилятором на этапе генерации кода. Команды очень длинны и содержат явные инструкции по распараллеливанию нескольких субкоманд на несколько устройств исполнения. Элементы архитектуры содержались в серии PA-RISC. VLIW-процессором в его классическом виде является Itanium. Разработка эффективного компилятора для VLIW является сложнейшей задачей. Преимущество VLIW перед суперскалярной архитектурой заключается в том, что компилятор может быть более развитым, нежели устройства управления процессора, и он способен хранить больше контекстной информации для принятия более верных решений по оптимизации.

Иные архитектурные решения, типичные для RISC

Спекулятивное исполнение. При встрече с командой условного перехода процессор исполняет (или, по крайней мере, читает в кэш инструкций) сразу обе ветви до тех пор, пока не окончится вычисление управляющего выражения перехода. Позволяет отказаться от простоев конвейера при условных переходах.

Переименование регистров. Каждый регистр процессора на самом деле представляет собой несколько параллельных регистров, хранящих несколько версий значения. Используется для реализации спекулятивного исполнения.

Начало развития RISC-архитектуры

Первая система, которая может быть названа RISC-системой, — суперкомпьютер CDC 6600, который был создан в 1964 году, за десять лет до появления соответствующего термина. CDC 6600 имел RISC-архитектуру всего с двумя режимами адресации («регистр+регистр» и «регистр+непосредственное значение») и 74 кодами команд (тогда как 8086 имел 400 кодов команд). В CDC 6600 было 11 конвейерных устройств арифметической и логической обработки, а также пять устройств загрузки и два устройства хранения. Память была многоблочной, поэтому все устройства загрузки-хранения могли работать одновременно. Базовая тактовая частота/частота выдачи команд была в 10 раз выше, чем время доступа к памяти. Джим Торнтон и Сеймур Крэй, разработчики CDC 6600, создали для него мощный процессор, позволявший быстро обрабатывать большие объёмы цифровых данных. Главный процессор поддерживался десятью простыми периферийными процессорами, выполнявшими операции ввода-вывода и другие функции ОС. Позднее появилась шутка, что термин "RISC" на самом деле расшифровывается как «Really invented by Seymour Cray» («на самом деле придуман Сеймуром Крэем»).

Ещё одна ранняя RISC-машина — миникомпьютер Data General Nova, разработанный в 1968 году.

Первая попытка создать RISC-процессор на чипе была предпринята в IBM в 1975 году. Эта работа привела к созданию семейства процессоров IBM 801, которые широко использовались в различных устройствах IBM. 801-й в конце концов был выпущен в форме чипа под именем ROMP в 1981 году. ROMP расшифровывается как Research OPD (Office Product Division) Micro Processor, то есть «исследовательский микропроцессор», разработанный в департаменте офисных разработок. Как следует из названия, процессор был разработан для «мини»-задач, и когда в 1986 году IBM выпустила на его базе компьютер IBM RT-PC, он работал не слишком хорошо. Однако за выпуском 801-го процессора последовало несколько исследовательских проектов, в результате одного из которых появилась система POWER.

Однако наиболее известные RISC-системы были разработаны в рамках университетских исследовательских программ, финансировавшихся программой DARPA VLSI.

Проект RISC в Университете Беркли был начат в 1980 году под руководством Дэвида Паттерсона и Карло Секвина. Исследования базировались на использовании конвейерной обработки и агрессивного использования техники регистрового окна. В обычном процессоре имеется небольшое количество регистров и программа может использовать любой регистр в любое время. В процессоре, использующем технологии регистрового окна, очень большое количество регистров (например, 128), но программы могут использовать ограниченное количество (например, только 8 в каждый момент времени).

Программа, ограниченная лишь восемью регистрами для каждой процедуры, может выполнять очень быстрые вызовы процедур: «окно» просто сдвигается к 8-регистровому блоку нужной процедуры, а при возврате из процедуры сдвигается обратно, к регистрам вызвавшей процедуры. (В обычном процессоре большинство процедур при вызове вынуждены сохранять значения некоторых регистров в стеке для того, чтобы пользоваться этими регистрами при исполнении процедуры. При возврате из процедуры значения регистров восстанавливаются из стека).

Проект RISC произвёл на свет процессор RISC-I в 1982 году. В нём было 44 420 транзисторов (для сравнения: в CISC-процессорах того времени их было около 100 тыс.). RISC-I имел всего 32 инструкции, но превосходил по скорости работы любой одночиповый процессор того времени. Через год, в 1983 году, был выпущен RISC-II, который состоял из 40 760 транзисторов, использовал 39 инструкций и работал в три раза быстрее RISC-I.

Практически в то же время, в 1981 году, Джон Хеннесси начал аналогичный проект, названный «MIPS-архитектура» в Стэнфордском университете. Создатель MIPS практически полностью сфокусировался на конвейерной обработке, попытавшись «выжать всё» из этой технологии. Конвейерная обработка использовалась и в других продуктах, некоторые идеи, реализованные в MIPS, позволили разработанному чипу работать значительно быстрее аналогов. Наиболее важным было требование выполнения любой из инструкций процессора за один такт. Это требование позволило конвейеру работать на гораздо бо́льших скоростях передачи данных и привело к значительному ускорению работы процессора. С другой стороны, исполнение этого требования имело негативный побочный эффект в виде удаления из набора инструкций таких полезных операций, как умножение или деление.

В первые годы попытки развития RISC-архитектуры были хорошо известны, однако оставались в рамках породивших их университетских исследовательских лабораторий. Многие в компьютерной индустрии считали, что преимущества RISC-процессоров не проявятся при использовании в реальных продуктах из-за низкой эффективности использования памяти в составных инструкциях. Однако с 1986 года исследовательские проекты RISC начали выпускать первые работающие продукты.

Последние годы

Как оказалось в начале 1990-х годов, RISC-архитектуры позволяют получить большую производительность, чем CISC, за счёт использования суперскалярного и VLIW-подхода, а также за счёт возможности серьёзного повышения тактовой частоты и упрощения кристалла с высвобождением площади под кэш, достигающий огромных ёмкостей. Также, RISC-архитектуры позволили сильно снизить энергопотребление процессора за счёт уменьшения числа транзисторов.

Первое время RISC-архитектуры с трудом принимались рынком из-за отсутствия программного обеспечения для них. Эта проблема была решена переносом UNIX-подобных операционных систем (SunOS) на RISC-архитектуры.

В настоящее время многие архитектуры процессоров являются RISC-подобными, к примеру, ARM, DEC Alpha, SPARC, AVR, MIPS, POWER и PowerPC. Наиболее широко используемые в настольных компьютерах процессоры архитектуры x86 ранее являлись CISC-процессорами, однако новые процессоры, начиная с Intel 486DX, являются CISC-процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции x86-процессоров в более простой набор внутренних инструкций RISC.

После того, как процессоры архитектуры x86 были переведены на суперскалярную RISC-архитектуру, можно сказать, что большинство существующих ныне процессоров основаны на архитектуре RISC.

-

![Обор Homatics Box Q и Homatics DONGLE Q]() 20:13, 30 марта 2021 | Новости, Обзоры ресиверов

Обор Homatics Box Q и Homatics DONGLE Q

20:13, 30 марта 2021 | Новости, Обзоры ресиверов

Обор Homatics Box Q и Homatics DONGLE Q

-

![Обзор AB CryptoBox 750HD + Xtra TV]() 18:09, 24 марта 2021 | Новости, Обзоры ресиверов

Обзор AB CryptoBox 750HD + Xtra TV

18:09, 24 марта 2021 | Новости, Обзоры ресиверов

Обзор AB CryptoBox 750HD + Xtra TV

-

![Обзор AB CryptoBox 800UHD DVB-S2X]() 14:35, 26 февраля 2021 | Новости, Обзоры ресиверов

Обзор AB CryptoBox 800UHD DVB-S2X

14:35, 26 февраля 2021 | Новости, Обзоры ресиверов

Обзор AB CryptoBox 800UHD DVB-S2X

-

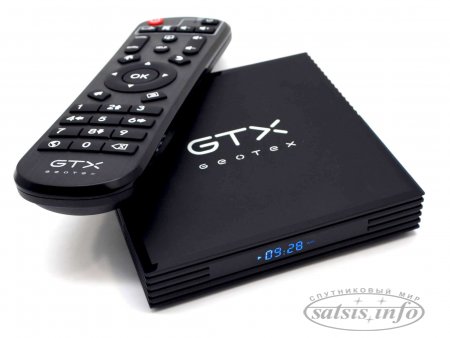

![Обзор Geotex GTX-R10i PRO]() 22:32, 15 октября 2020 | Новости, Обзоры ресиверов

Обзор Geotex GTX-R10i PRO

22:32, 15 октября 2020 | Новости, Обзоры ресиверов

Обзор Geotex GTX-R10i PRO

-

![Обзор Formuler Z8]() 13:24, 11 июля 2019 | Новости, Обзоры ресиверов

Обзор Formuler Z8

13:24, 11 июля 2019 | Новости, Обзоры ресиверов

Обзор Formuler Z8

-

![Осторожно, Zidoo]() 14:23, 14 февраля 2019 | Новости, Обзоры ресиверов

Осторожно, Zidoo

14:23, 14 февраля 2019 | Новости, Обзоры ресиверов

Осторожно, Zidoo

-

![Обзор Sat-Integral 5052 T2]() 15:59, 10 декабря 2018 | Обзоры ресиверов

Обзор Sat-Integral 5052 T2

15:59, 10 декабря 2018 | Обзоры ресиверов

Обзор Sat-Integral 5052 T2

-

![Власти Южной Кореи готовы выделить $7,3 млрд на поддержку национальной полупроводниковой отрасли]() 06:29, 12 мая 2024 | Новости

Власти Южной Кореи готовы выделить $7,3 млрд на поддержку национальной полупроводниковой отрасли

06:29, 12 мая 2024 | Новости

Власти Южной Кореи готовы выделить $7,3 млрд на поддержку национальной полупроводниковой отрасли

-

![Samsung форсирует выход на рынок стеклянных подложек для чипов]() 06:29, 12 мая 2024 | Новости

Samsung форсирует выход на рынок стеклянных подложек для чипов

06:29, 12 мая 2024 | Новости

Samsung форсирует выход на рынок стеклянных подложек для чипов

-

![Маск заявил, что четвертый испытательный полет Starship может состояться через 3-5 недель]() 06:26, 12 мая 2024 | Новости

Маск заявил, что четвертый испытательный полет Starship может состояться через 3-5 недель

06:26, 12 мая 2024 | Новости

Маск заявил, что четвертый испытательный полет Starship может состояться через 3-5 недель

-

![Tak TV тестируется на 4,8°E]() 06:24, 12 мая 2024 | Новости

Tak TV тестируется на 4,8°E

06:24, 12 мая 2024 | Новости

Tak TV тестируется на 4,8°E

-

![На Земле началась очень сильная магнитная буря]() 06:19, 12 мая 2024 | Новости

На Земле началась очень сильная магнитная буря

06:19, 12 мая 2024 | Новости

На Земле началась очень сильная магнитная буря

-

![Канал Настоящее Время в FTA на 9°E]() 06:16, 12 мая 2024 | Новости

Канал Настоящее Время в FTA на 9°E

06:16, 12 мая 2024 | Новости

Канал Настоящее Время в FTA на 9°E

-

![Запущена новая группа спутников Starlink]() 21:11, 10 мая 2024 | Новости

Запущена новая группа спутников Starlink

21:11, 10 мая 2024 | Новости

Запущена новая группа спутников Starlink

XML error in File: https://www.tricolor.tv/rss/

Футбол

21:45 Фіорентина

Обновлено: 21:07 13.05.2024

Телепрограмма

18:55 - "Супермама", 9 сезон, 2 эп. "Угрожала любовнице мужа, чтобы вернуть его в семью".

20:00 - Т/с "Доктор Ковальчук", 3 сезон, 3 с.

20:55 - Т/с "Доктор Ковальчук", 3 сезон, 4 с.

20:00 -

22:10 - Баскетбол. Чемпионат Испании. АБК Лига. Обзор.

22:30 - Гандбол. Чемпионат Германии. Бундеслига. Фленсбург-Хандевитт - Мельзунген.

19:00 - "Единые новости". Телемарафон.

20:00 - "Единые. Главное". Итоговые новости.

21:00 - "Единые новости". Телемарафон.

19:30 - Х/ф "Артур, ты король".

21:15 - Х/ф "Игра киллеров".

22:50 - Х/ф "Память".

Вся телепрограмма

Голосование

Какой диагонали у вас телевизор

Кто онлайн

Новое в каталоге

Sat-integral club

Re: ПО Sat-Integral S-1218-28HD / S-1248-58-68HD / S-1311 HD COMBO v3.47

Re: ПО Sat-Integral S-1218-28HD / S-1248-58-68HD / S-1311 HD COMBO v3.47

Re: ПО Sat-Integral S-1218-28HD / S-1248-58-68HD / S-1311 HD COMBO v3.47

Re: ПО Sat-Integral S-1218-28HD / S-1248-58-68HD / S-1311 HD COMBO v3.47

Re: Безкоштовний плейлист IPTV

PHP: mail() через внешние SMTP msmtp

webhook telegram Read timeout expired

Блокировка интернета на PS4 или ПК детям, через Telegram бота на Mikrotik

Сервер VPN IKEv2 MSCHAPv2 с логином и паролем на MikroTik + клиент Android 13

Уведомление в Telegram об окончании бекапа Hestia или VestaCP

Бесплатный VPN Warp от Cloudflare на роутере Keenetic Speedster

Windows 10 Неверное имя пользователя и пароль Samba Share Ubuntu

Host key verification failed после обновления сервера Ubuntu

dhcp-client on ISP1 lost IP address 176.117.167.211 — lease stopped locally

NFS подключение диска windows client к серверу на Ubuntu